射頻集成電路是連接數(shù)字世界與無(wú)線物理世界的橋梁,廣泛應(yīng)用于智能手機(jī)、物聯(lián)網(wǎng)、衛(wèi)星通信等領(lǐng)域。其設(shè)計(jì)融合了模擬電路、數(shù)字電路與高頻電磁場(chǎng)理論,復(fù)雜度極高,工程師在設(shè)計(jì)過程中常面臨一系列挑戰(zhàn)。本文將系統(tǒng)性地探討射頻集成電路設(shè)計(jì)中的幾個(gè)核心難題,并提供相應(yīng)的解決思路與方案。

一、 常見問題分析

- 噪聲與線性度之間的權(quán)衡: 這是射頻設(shè)計(jì)永恒的矛盾。低噪聲放大器需要工作在低偏置電流以最小化噪聲,但這會(huì)犧牲線性度,導(dǎo)致處理大信號(hào)時(shí)產(chǎn)生失真。反之,提高線性度往往引入更多噪聲。

- 阻抗匹配與帶寬限制: 射頻信號(hào)對(duì)阻抗極其敏感。實(shí)現(xiàn)50歐姆的寬帶阻抗匹配非常困難,尤其是在片上集成的電感、電容參數(shù)受工藝偏差影響較大的情況下。窄帶匹配容易實(shí)現(xiàn),但限制了電路的應(yīng)用范圍。

- 寄生效應(yīng)與隔離度: 在高頻下,導(dǎo)線電感、襯底耦合、封裝寄生等效應(yīng)變得不可忽視。電源線與信號(hào)線之間的耦合、不同電路模塊之間的串?dāng)_(如本振泄漏到射頻端口),會(huì)嚴(yán)重惡化系統(tǒng)性能,如接收機(jī)靈敏度、發(fā)射機(jī)頻譜純度等。

- 工藝波動(dòng)與模型不準(zhǔn): 先進(jìn)半導(dǎo)體工藝的器件尺寸不斷縮小,工藝波動(dòng)對(duì)射頻性能(如截止頻率、噪聲系數(shù))的影響加劇。高頻下的器件模型(特別是無(wú)源器件如電感、變壓器)往往不夠精確,導(dǎo)致仿真與實(shí)測(cè)結(jié)果存在差距。

- 功耗與性能的平衡: 移動(dòng)設(shè)備對(duì)功耗有嚴(yán)苛要求。如何在滿足增益、線性度、噪聲等指標(biāo)的前提下,盡可能降低功耗,是設(shè)計(jì)中的一大挑戰(zhàn)。

二、 核心解決方案與設(shè)計(jì)策略

針對(duì)上述問題,現(xiàn)代射頻IC設(shè)計(jì)發(fā)展出多種應(yīng)對(duì)策略:

- 架構(gòu)級(jí)優(yōu)化:

- 噪聲與線性度: 采用電流復(fù)用、噪聲消除、導(dǎo)數(shù)疊加等技術(shù)。例如,在低噪聲放大器中使用并聯(lián)反饋或共源共柵結(jié)構(gòu),可以在一定范圍內(nèi)改善線性度而不顯著增加噪聲。對(duì)于混頻器等模塊,可采用無(wú)源混頻器或電流導(dǎo)引結(jié)構(gòu)來獲得更好的線性度。

- 系統(tǒng)規(guī)劃: 合理分配系統(tǒng)級(jí)聯(lián)中各模塊的增益、噪聲和線性度指標(biāo),避免某個(gè)模塊成為性能瓶頸。利用先進(jìn)的數(shù)字校準(zhǔn)和預(yù)失真技術(shù)來補(bǔ)償模擬電路的線性度不足。

- 電路與版圖協(xié)同設(shè)計(jì):

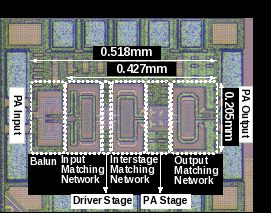

- 阻抗匹配: 使用片上自動(dòng)調(diào)諧網(wǎng)絡(luò)、可編程電容陣列等自適應(yīng)匹配技術(shù)來應(yīng)對(duì)工藝偏差和頻率變化。采用多級(jí)匹配或?qū)拵ヅ渫負(fù)洌ㄈ绶植际椒糯笃鳎﹣硗卣箮挕?/li>

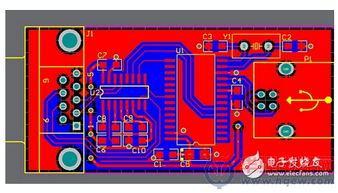

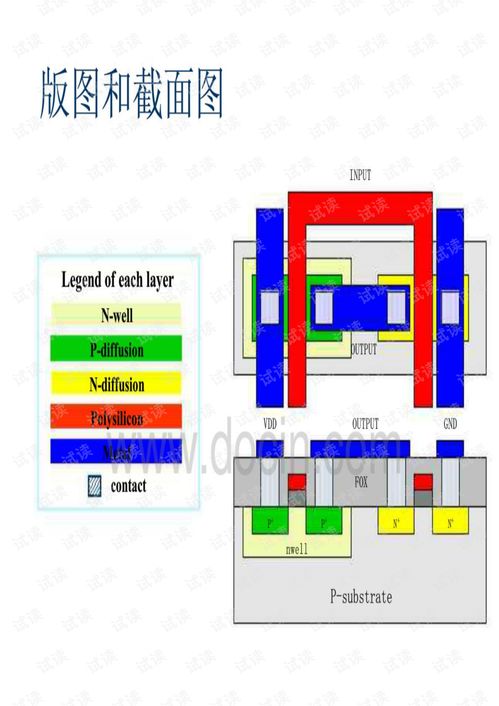

- 隔離與抗寄生: 在版圖上,大量使用保護(hù)環(huán)、深N阱隔離、接地屏蔽層來減少襯底耦合。對(duì)敏感線路采用差分走線。電源線必須精心設(shè)計(jì)去耦網(wǎng)絡(luò),使用高質(zhì)量(高Q值)的片上電容和封裝上的分立電容組合。將數(shù)字與射頻模塊物理隔離,并采用獨(dú)立的電源域和接地。

- 模型與工藝的深度結(jié)合:

- 設(shè)計(jì)前期: 與晶圓代工廠緊密合作,獲取更精確的射頻工藝設(shè)計(jì)套件,特別是針對(duì)無(wú)源元件的電磁仿真模型。

- 設(shè)計(jì)后期: 必須進(jìn)行全芯片的電磁聯(lián)合仿真,以評(píng)估大信號(hào)下的耦合效應(yīng)。采用蒙特卡洛分析來評(píng)估工藝角變化對(duì)性能的影響,并在設(shè)計(jì)中預(yù)留足夠的裕量或可調(diào)單元。

- 低功耗設(shè)計(jì)技術(shù):

- 采用亞閾值或弱反型區(qū)設(shè)計(jì)技術(shù),在極低電壓電流下工作。

- 設(shè)計(jì)高性能的電源管理單元,為射頻電路提供多路可調(diào)、低噪聲的電源。

- 利用電路休眠、功率分級(jí)等系統(tǒng)策略,根據(jù)通信需求動(dòng)態(tài)調(diào)整射頻前端的功耗。

三、 未來趨勢(shì)與

隨著5G/6G、毫米波通信和硅基工藝的持續(xù)演進(jìn),射頻集成電路設(shè)計(jì)正朝著更高頻段、更寬帶寬、更高集成度和更智能化方向發(fā)展。面臨的挑戰(zhàn)將更加嚴(yán)峻,但解決方案也在不斷革新。例如,利用人工智能輔助進(jìn)行電路優(yōu)化和版圖生成,采用異構(gòu)集成(如將GaAs、SiGe與CMOS集成)來獲得最佳性能,以及通過系統(tǒng)級(jí)封裝技術(shù)來整合最優(yōu)的射頻單元。

總而言之,成功的射頻集成電路設(shè)計(jì)沒有單一的“銀彈”,它要求工程師深刻理解高頻物理、電路原理、半導(dǎo)體工藝和系統(tǒng)應(yīng)用,并在復(fù)雜的多目標(biāo)約束中做出精巧的權(quán)衡與創(chuàng)新。通過架構(gòu)創(chuàng)新、精心設(shè)計(jì)與先進(jìn)工具的緊密結(jié)合,才能攻克難題,打造出高性能、高可靠的射頻芯片。